Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Логические устройства разделяют на два класса: комбинационные и последовательностные.

Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Выходные сигналы последовательностных устройств определяются не только сигналами, имеющимися на входах в данный момент времени, но и состоянием элементов памяти. Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы.

y3

Дешифраторы

Дешифратор (decoder) – это комбинационное устройство, позволяющее распознавать числа, представленные позиционным п-разрядным кодом. Если на входе дешифратора «-разрядный двоичный код, то на его выходе код «1 из Ν». В кодовой комбинации этого кода только одна позиция занята единицей, а все остальные – нулевые. Например, код «1 из Ν», содержащий 4 кодовые комбинации, будет представлен следующим образом:

Дешифраторы применяют для расшифровки адресов ячеек запоминающих устройств, высвечивания букв и цифр на мониторах, индикаторах и других устройствах. Чаще всего они являются встроенными в БИС, как, например, в полупроводниковых запоминающих устройствах, однако они выпускаются и в виде ИС среднего уровня интеграции.

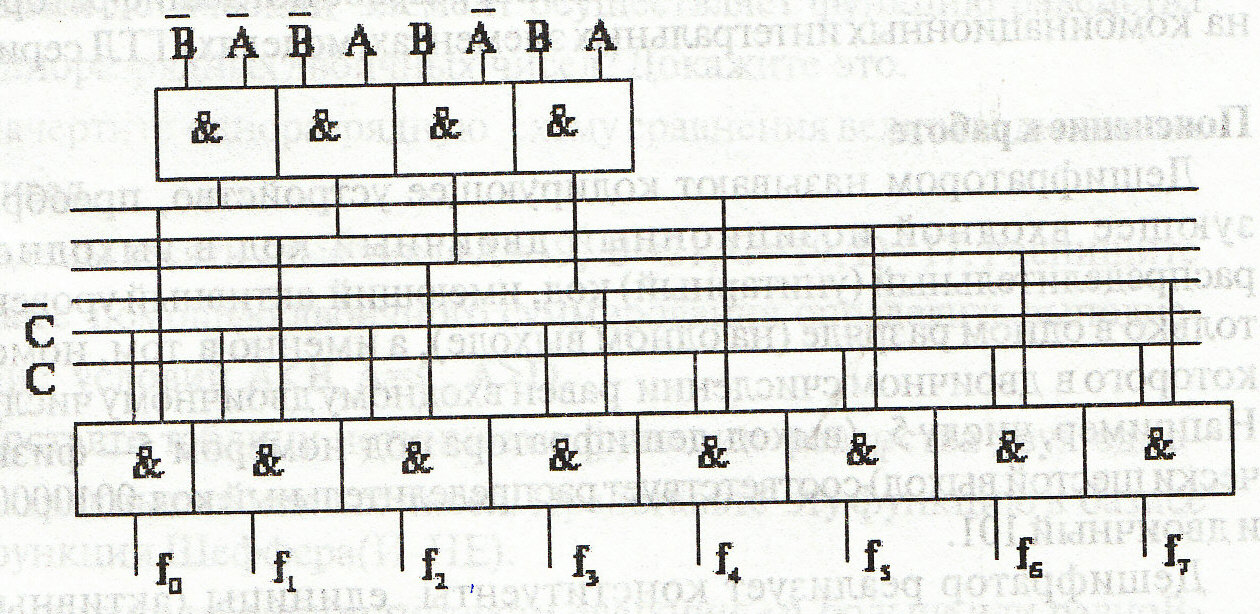

Проиллюстрируем реализацию дешифраторов на примере полного дешифратора трехразрядных чисел. Таблица истинности дешифратора представлена в табл. 3.5.

Таблица 3.5

x3

x2

x1

y0

y1

y2

y3

y4

y5

y6

y7

Как видно, каждый выход xi равен единице только на одном наборе, поэтому работа дешифратора описывается восемью функциями – по числу выходов дешифратора, каждая из которых является конъюнкцией (логическим И) трех аргументов:

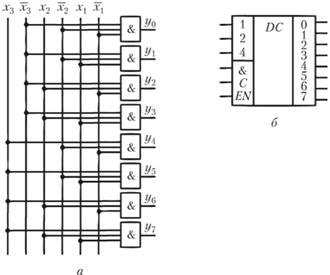

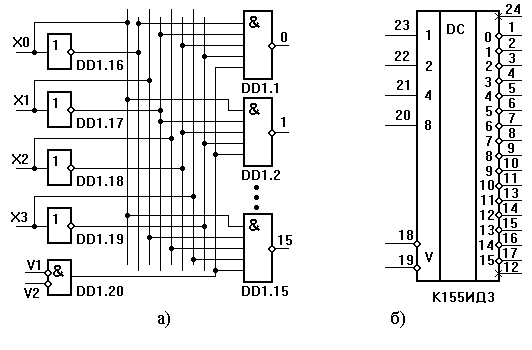

Схема трехразрядного полного дешифратора показана на рис. 3.12. Для реализации одной функции yi, нужен один трехвходовый конъюнктор. Так как на входах конъюнкторов присутствуют как прямые значения аргументов, так и инверсные, в схеме дешифратора необходимы три инвертора (см. рис. 3.12, а).

Рис. 3.12. Линейный дешифратор на три входа:

а – логическая схема; б – условное обозначение дешифратора с входами синхронизации и разрешения

Число контактов у стандартного корпуса несложной ИС ограничено (14, 16 или 24), поэтому дешифраторы, выпускаемые в виде ИС, имеют небольшую разрядность входного кода (три, реже четыре). Так, например, в 16-контактном корпусе может быть помещен лишь трехразрядный полный дешифратор. Если требуется создать дешифратор большей разрядности, используют каскадное соединение дешифраторов небольшой разрядности.

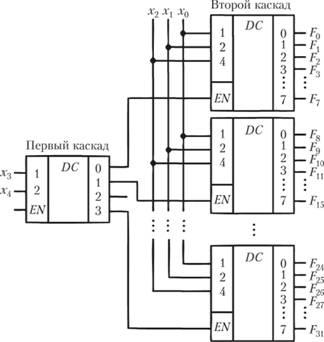

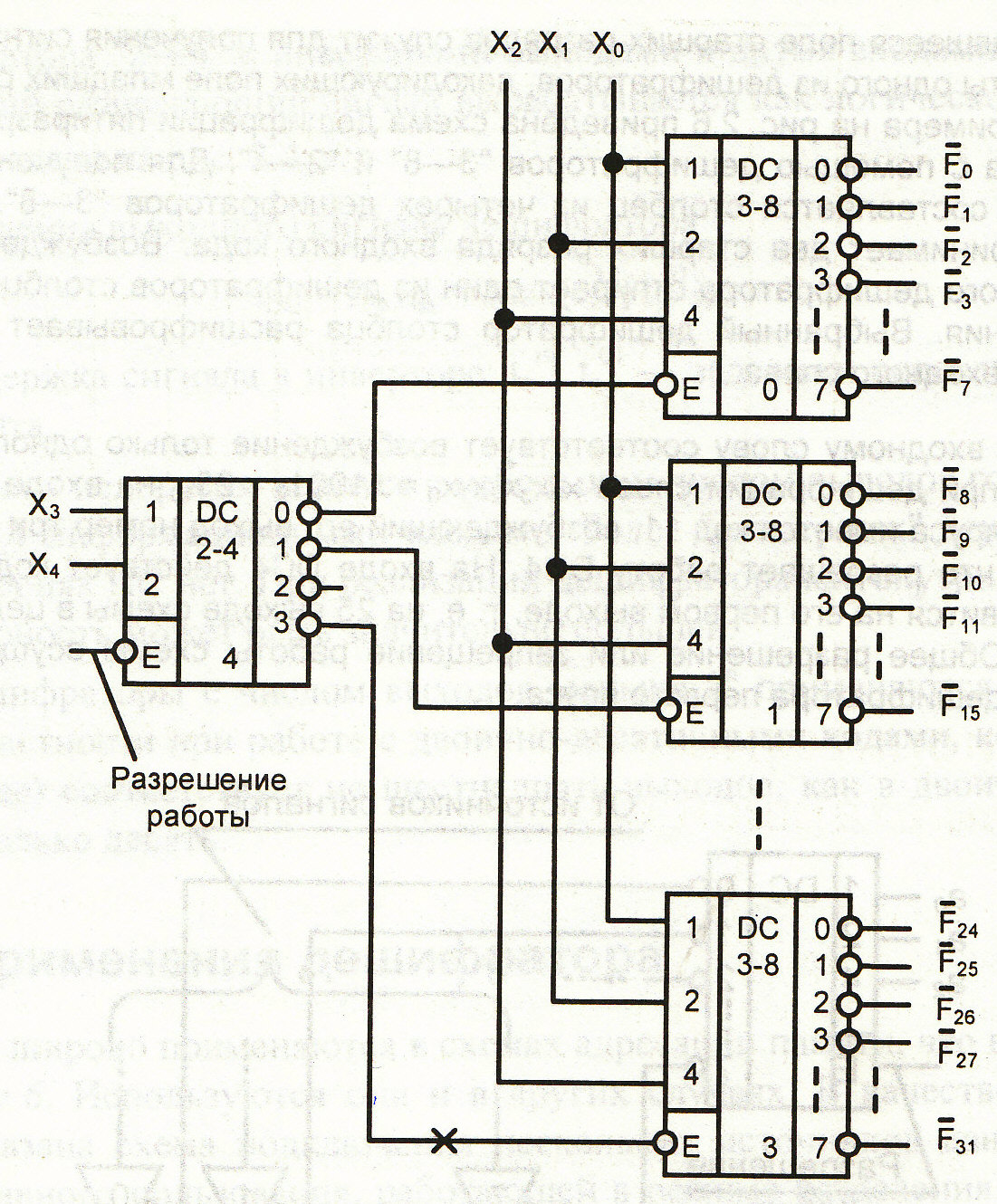

Пример 3.1. Пусть на основе трехразрядных дешифраторов необходимо создать пятиразрядный (рис. 3.13).

Рис. 3.13. Схема наращивания размерности дешифратора

Пусть, например, входной код равен 11011 = 2710. Так как старшие разряды – «11», то управляющий дешифратор разрешит работу 4-го дешифратора второго каскада. При этом на выходах первых трех дешифраторов будут нули, а на выходе «3» четвертого дешифратора, т.е. F27 будет логическая единица.

Рис. 3.14. Схема управления исполнительными устройствами технологической системы на основе дешифратора

Вход X(1:0)

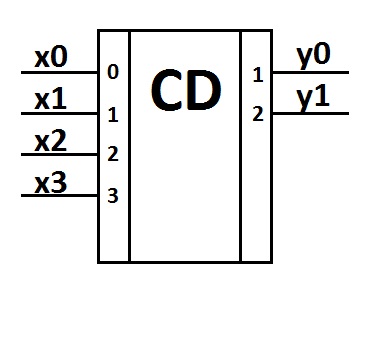

Шифратор – это комбинационное цифровое логическое устройство преобразующее номер входного сигнала в выходной двоичный код. Т.е. выполняет функцию обратную дешифратору.

Полный двоичный шифратор имеет n выходов и 2 n входов, где n – разрядность двоичного входа (см. рис.1).

Рис.1. УГО шифратора 4х2

Микросхемы шифраторов обозначаются на схемах буквами «CD» (от англ. Coder – кодирующее устройство). Рассмотрим таблицу истинности классического шифратора (см. табл. 1).

Вход х(3:0)

Выход y(1:0)

Таблица 1. Таблица истинности шифратора 4х2

Из таблицы истинности видно, что на выходе «y(1:0)» отображается номер входа, на котором установлена логическая единица.

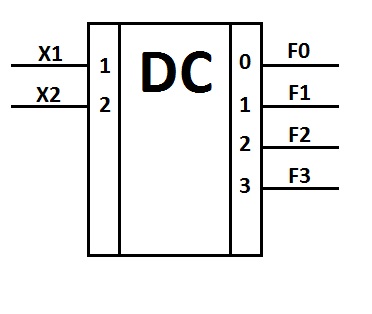

Дешифратор преобразует входной двоичный код в управляющий сигнал только на одном из своих выходов. В общем случае, дешифратор имеет n однофазных выходов и 2 n выходов, где n – разрядность дешифрируемого кода.

Блок дешифратора на схеме обозначаются буквами «DC» (от англ. Decoder – декодирующее устройство) (см.рис.2).

Рис.2. УГО дешифратора 2х4

Активным всегда является только один выход дешифратора, при этом номер этого выхода и соответствующий номер этого сигнала однозначно определяется входным кодом. Т.е. при сигнале на входе дешифратора 00 мы получаем 1 на нулевом выходе. При сигнале на входе 01 получаем 1 на первом выходе. При сигнале на входе 10, получаем 1 на втором выходе, и т.д. (см. табл. истинности табл.2).

Вход X(1:0)

Выход F(3:0)

Одно из применений дешифраторов – управление светодиодными индикаторами. Дешифратор ИД9 предназначен для управления неполной светодиодной матрицей .

Дешифратором называют преобразователь двоичного n-разрядного кода в унитарный позиционный 2n-разрядный код, все разряды которого, за исключением одного, равны нулю. Де-шифраторы бывают полные и неполные.

Для полного дешифратора выполняется условие:

N = 2n, где n – число входов, N – число выходов.

Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, на-пример, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а имеющий только 10 выходов является неполным. В условном обозначении дешифраторов используются буквы DC (от англ. Decoder).

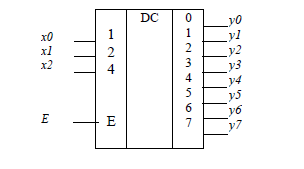

Входы дешифраторов принято обозначать их двоичными весами. Кроме информационных входов дешифратор имеет один или более входов разрешения работы обозначаемых как Е (Enable). При наличии разрешения по этому входу дешифратор работает описанным образом, при его отсутствии все выходы де-шифратора пассивны.

Рис 20.1 приведено условное обозначение дешифратора, имеющего два двоичных входа и четыре выхода. Работа этого дешифратора описывается следующими логическими функция-ми:

Условное графическое обозначение дешифратора (а) и схема его реализации (б) Из анализа этих соотношений следует, что рассматривае-мый дешифратор преобразовывает каждое двоичное двухразрядное число в одну логическую единицу на соответствующем выходе. Такие дешифраторы широко ис-пользуются в устройствах вывода цифровой информации, для индикации двоичного числа в десятичном виде, для определения адресной шины в микросхемах памяти и т.п.

Функциональная схема дешифратора, составленная на ос-нове записанных выше логических функций, показана на рис. 20.1, б.

С помощью инверторов, включенных на входе дешифра-тора, на внутренней шине данных дешифратора формируется полный набор логических сигналов:

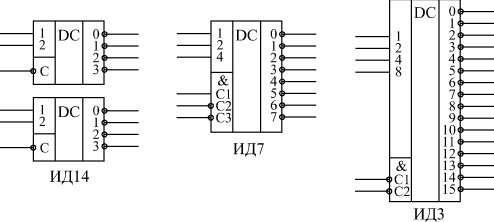

С использованием элемента И формируются соответствующие выходные сигналы. Описанный дешифратор реализован на микросхеме КР531ИД14, которая представляет собой два преобразователя 2х4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, а также инверсный вход разрешения Е (рис. 20.2).

line-height:130%» align=»center»>Рис. 20.2. ИМС КР531ИД14

Цифры на входе (1, 2) обозначают вес разряда двоичного числа, а цифры на выходе (0, 1, 2, 3) определяют десятичное число, соответствующее заданному числу на входе.

При логической 1 на входе разрешения на всех выходах будут также логические 1. При активизации входа разрешения, т. е. при Е = 0, логический 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданного на информационные входы.

В качестве неполного дешифратора можно привести микросхему К555ИД6 (рис. 20.3).

line-height:130%» align=»center»>Рис. 20.3. Дешифратор К555ИД6

Дешифратор имеет 4 прямых входа, обозначенных через А1,А2,А4,А8(адресных) и 10 инверсных выходов. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе.

Например, если на всех входах – логические нули, то на выходе Y0– логический ноль, а на остальных выходах – логическая единица.

Если на входе А2– логическая единица, а на остальных входах — логический ноль, то на выходе Y2 – логический ноль, а на остальных выходах — логическая единица.

Если на входе – двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах – логическая единица.

Благодаря наличию входа разрешения можно наращивать размерность дешифраторов. Так, используя 5 дешифраторов 2х4, можно построить дешифратор4х16 (рис. 20.4).

line-height:130%» align=»center»>Рис. 20.4. Дешифратор 4х16

Схема работает следующим образом. Например, при подаче на вход числа 0100 (двоичный эквивалент десятичного числа 4) и при Е = 0 логический 0 появится лишь на втором (сверху) выходе дешифратора DC1, а на всех остальных выходах будут логические 1.

Это приведет к активизации лишь дешифратора DC3 и активизируется (появится логический 0) лишь его верхний выход, что и будет соответствовать десятичному числу 4.

При подаче на вход числа 1111 будет активизирован дешифратор DC5 и на его нижнем выходе появится логический 0, что будет соответствовать десятичному числу 15.

Очевидно, что если использовать две микросхемы КР531ИД14, т. е. четыре дешифратора 2х4, можно построить неполный дешифратор.

Рассмотрим принцип расширения разрядности дешифраторов на примере полного четырехразрядного дешифратора.

Принцип работы и построения 8-разрядного DС следующий. Производится разделение кода дешифрируемого числа на две части по 4 разряда, младшие Х3,Х2,Х1,Х0 старшие Х7,Х6,Х5,Х4.

130%»>Код, определяемый комбинацией старших переменных, обусловливает выбор одного из шестнадцати дешифраторов. Например, если на вход поступает код Х7Х6Х5Х4Х3Х2Х1Х0=11110010, то старшие четыре разряда, поступая на входы DСY, приводят к появлению сигнала логического нуля на 15-м выходе DСY, так как 11112 = 1510, следовательно, переводится в рабочий режим DС15.

Младшие разряды, которые одновременно поступают на DС0. DС15, обусловливают возбуждение второго выхода DС, так как 00102 = 210. Результат определяется как сумма 111100002 = 24010 и 00102 = 210, т.е. 111100102 =24210. Остальные выходы всех дешифраторов находятся при этом в состоянии логической единицы.

Схема восьмиразрядного дешифратора приведена на рис. 20.5.

Дешифратор – одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств. Это обусловлено тем, что на выходе дешифратора вырабатываются все возможные логические произведения всех входных переменных. Подключая к определенным выводам дешифратора логический элемент ИЛИ или используя дешифратор с открытым выходом и реализуя на нем «монтажное ИЛИ», можно реализовать любую логическую функцию.

Одно из применений дешифраторов – управление светодиодными индикаторами. Дешифратор ИД9 предназначен для управления неполной светодиодной матрицей .

Матрица состоит из дискретных светодиодов, рассчитанных на прямой ток 10 мА.

Структурная схема трехразрядного дешифратора, синтезированная на основании полученных ФАЛ приведена на рис. 1, а, а его УГО — на рис. 1, б.

Соответствующие таблице истинности ФАЛ имеют вид:

Структурная схема трехразрядного дешифратора, синтезированная на основании полученных ФАЛ приведена на рис. 1, а, а его УГО — на рис. 1, б.

Рис. 1.Структурная схема и УГО трехразрядного дешифратора.

В общем случае логические уравнения для выходных переменных дешифратора n-разрядного числа имеют вид:

Рис. 2. Пирамидальный дешифратор для трехразрядного числа.

Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Также как и дешифраторы, шифраторы бывают полными и неполными. Работа восьмивходового полного шифратора задается следующей таблицей истинности:

На основании таблицы истинности можно записать ФАЛ, задающие работу восьмивходового шифратора:

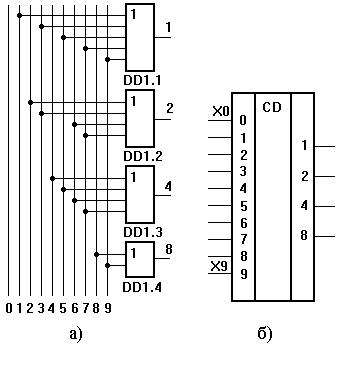

Синтезированная на основании приведенных логических уравнений структурная схема шифратора представлена на рис. 3,а, а его условное графическое обозначение – на рис. 3,б.

Рис. 3.Структура и УГО восьмивходового шифратора.

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Шифратор осуществляет преобразование десятичных чисел в двоичную систему счисления. На рис.9.9 приведено символическое изображение шифратора, преобразующего десятичные числа 0, 1, 2, … , 9 в выходной код 8421 и его таблица истинности. Символ CD образован из букв английского слова Coder. Слева показаны 10 входов шифратора, справа – выходы шифратора; цифрами 1,2,4,8 обозначены весовые коэффициенты двоичных четырёх разрядов шифратора.

Из таблицы истинности видно, что выходу x1 будет соответствовать лог. 1, если одна из входных переменных y1, y3, y5, y7, y9 будет также иметь лог. 1. Следовательно, можно составить логическую операцию x1=y1 y3 y5 y7 y9. Для остальных выходов можно составить логические операции: x2=y2 y3 y6 y7, x4=y4 y5 y6 y7, x8=y8 y9.

Рис.9.9. Символическое изображение шифратора и его таблица истинности

Используя полученные логические операции, можно реализовать логическую схему шифратора, построенную на логических элементах ИЛИ, приведённую на рис.9.10. Шифраторы используются в устройствах ввода информации в цифровые системы с клавиатуры.

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов ивыходов в полном шифраторе связано соотношением п = 2 т , где п — число входов, т — число выходов.

Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подаётся только на один вход.Условное обозначение шифратора и таблица соответствия кода.

Схема такого шифратора, на элементах ИЛИ.

На практике часто используют шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал «1», т. е. на приоритетный шифратор допускается подавать сигналы на несколько входов, а он выставляет на выходе код числа, соответствующего старшему входу.

Рассмотрим в качестве примера шифратор с приоритетом (приоритетный шифратор) К555ИВЗ серии микросхем К555 (ТТЛШ). Шифратор имеет 9 инверсных входов, обозначенных через PRI. PR9. Аббревиатура PR обозначает «приоритет». Шифратор имен четыре инверсных выхода В1, . , B8. Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, В8 обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор.

Если на всех входах — логическая единица, то на всех выходах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111).Если хотябы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номе ром входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер.

Например, если на входе PRI — логический ноль, а на всех остальных входах — логическая единица, то на выходах имеются следующие сигналы: В1 — 0, В2 -1, В4-1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

Обратимся для примера к дешифраторуК555ИД6. Дешифратор имеет 4 прямых входа,обозначенных через А1, . A8. Аббревиатура А обозначает «адрес» (от англ. address). Указанные входы называю т адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа.

Дешифратор имеет 10 инверсных выходов Y0, . ,Y9. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Помимо информационных имеется один или более входов, называемых входами разрешения, или адресными входами. Так, микросхема КР531ИД14 представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, атакже инверсный вход разрешения.

Цифры на входе (1,2) обозначают вес разряда двоичного числа, а цифры на выходе (0-3) определяют десятичное число, соответствующее заданному числу на входе.

При логической 1 на входе разрешения на всех выходах будут также логические 1. При активизации входа разрешения, т. е. при Е = 0, логический 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданного на информационные входы. Благодаря наличию входа разрешения можно наращивать размерность дешифраторов. Так, используя 5 дешифраторов 2×4, можно построить дешифратор 4×16.

Очевидно, что если использовать две микросхемы КР531ИД14, т. е. четыре дешифратора 2×4, можно построить неполный дешифратор.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Это основано на том обстоятельстве, что на выходе дешифратора вырабатываются все возможные логические произведения всех входных переменных (конъюнктивные минтермы).

Подключая к определенным выводам дешифратора логический элемент ИЛИ или используя дешифратор с открытым выходом и реализуя на нем «монтажное ИЛИ», можно реализовать любую логическую функцию.

Дешифратор — это комбинационный узел или комбинационная схема, имеющая при n информационных входах до 2n выходов и осуществляющая преобразование параллельного двоичного числа в унитарный код.

Дешифратор — это комбинационный узел или комбинационная схема, имеющая при n информационных входах до 2n выходов и осуществляющая преобразование параллельного двоичного числа в унитарный код.

В стандартные серии входят дешифраторы на 4 выхода (2 разряда входного кода), на 8 выходов (3 разряда входного кода) и на 16 выходов (4 разряда входного кода). Они обозначаются соответственно как 2-4, 3-8, 4-16. Различаются микросхемы дешифраторов входами управления (разрешения/запрета выходных сигналов), а также типом выхода: 2С или ОК.

Выходные сигналы всех дешифраторов имеют отрицательную полярность. Входы, на которые поступает входной код, называют часто адресными входами. Обозначают эти входы 1, 2, 4, 8, где число соответствует весу двоичного кода (1 — младший разряд, 2 — следующий разряд и т.д.), или А0, А1, А2, А5. В отечественных сериях микросхемы дешифраторов обозначаются буквами ИД. На (рис. 4) показаны три наиболее типичных микросхемы дешифраторов.

Рисунок 4 Примеры микросхем дешифраторов.

y0 = E ? x2 ? x1? x0 ; y1 = E ? x2 ? x1? x0 ;

y2 = E ? x2 ? x1? x0; y3 = E ? x2 ? x1? x0 ;

y4 = E ? x2 ? x1? x0; y5 = E ? x2 ? x1? x0 ;

y6 = E ? x2 ? x1? x0 ; y7 = E ? x2 ? x1? x0.

Используя полученные выражения, можно предложить соответствующее условное изображение дешифратора, у которого активными сигналами на выходах являются единицы (рис. 5)

Рисунок 5 Условное графическое обозначение дешифратора с активными единичными сигналами на выходах и входе E

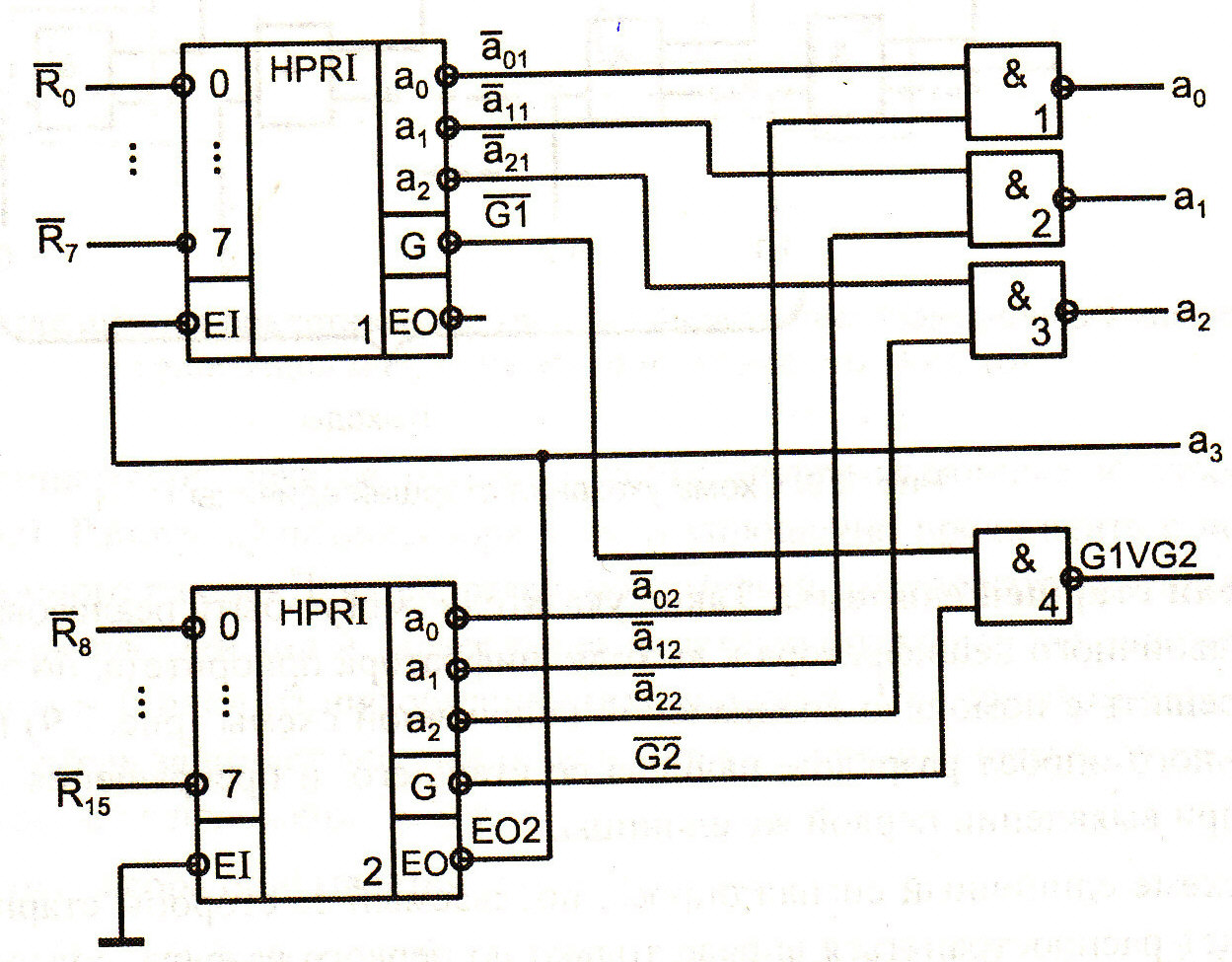

Два приоритетных шифратора 6 на 3, работающих на три общие линии с логикой подключения выходов к линии.

Лабораторная работа №1

Схемотехника дешифраторов и шифраторов.

Цель работы:

Изучение принципа работы и типов дешифраторов и шифраторов.

Синтез дешифраторов и шифраторов произвольной разрядности с использованием микросхем.

Разработка навыков применения справочников по интегральным схемам при решении прикладных задач.

Теоретическая часть

Дешифратор это устройство, преобразующее входной двоичный код в выходной унитарный код, имеющий активный уровень только в одном разряде на выходе, а именно в том, номер которого в двоичном счислении равен входному двоичному числу.

Логика работы Интегральное исполнение

Рисунок 1 – Дешифратор 4 на 16

При линейной организации (на примере 3-8, рисунок 2) каждый минтерм реализуется отдельно на трех входовом элементе типа И. На входы элементов подаются все возможные комбинации прямых и инверсных значений разрядов входного кода. Для каждого значения входного кода будет активироваться один выход.

Рисунок 2 – Линейный дешифратор

Пример пирамидальной структуры дешифратора показан на рисунке 3. При этом первый уровень пирамиды формирует все возможные конъюнкции двух разрядов, а второй уровень пирамиды формирует возможные конъюнкции выходов первого ряда схем следующего разряда. Уровней пирамиды может несколько.

Рисунок 3 – Пирамидальный дешифратор

Рисунок 4 – Принцип наращивания разрядности дешифратора

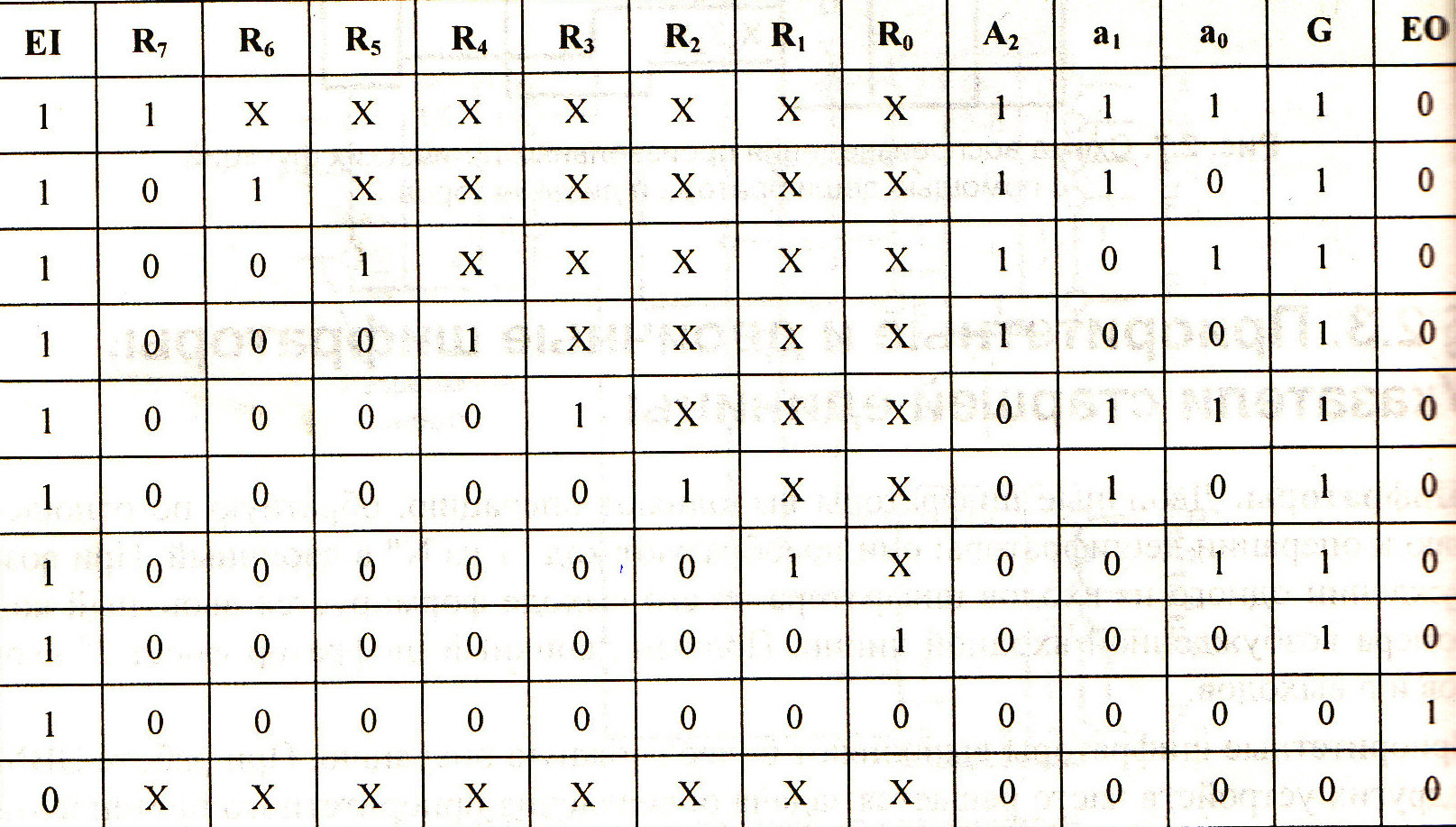

Таблица 1 – Таблица состояний приоритетного шифратора.

Рисунок 5 – Неполный шифратор

Входами приоритетного шифратор являются (по таблице 1) R0-R7, вход разрешения работы Е1, выходы А0-А2, выход G – признак наличия комбинации входного кода, выход EO – признак отсутствия комбинации кода на входе. Основной особенностью приоритетного шифратора является соответствие каждой унитарной комбинации входа уровню приоритета. На рисунке 6 показан принцип наращивания размерности приоритетного шифратора.

Рисунок 6 – Принцип наращивания разрядности шифратора

Приоритетные шифраторы используются при решении задачи определения приоритетного претендента на использование каким-либо ресурсом, в частности они используются в контроллерах прерываний в качестве арбитров приоритета запроса.

Задание на лабораторную работу

Разработать электрическую функциональную и электрическую принципиальную схемы согласно вариантам

Microsoft — Visio

схем ы

Дешифратор линейного типа и

дешифратор пирамидального типа 4-14, выходы инверсные.

Приоритетный шифратор на 6 входов и 3 выхода, входы инверсные

Дешифратор пирамидального типа 5-20, выходы инверсные

выбрать самостоятельно по

критерию минимального количества корпусов

Дешифратор 6 на 40

Соединенные дешифратор 3-8 и шифратор 8-3, предусмотреть сигнал разрешения работы шифратора

выбрать самостоятельно по

критерию минимума корпусов

Дешифратор 4 на 16 с инверсными входами

Шифратор 4 на 2, входы и выходы инверсные, предусмотреть сигнал разрешения работы схемы

выбрать самостоятельно, обосновать

Соединенная пара (шифратор 5 на 3, дешифратор 3-8) входы шифратора инверсные, выходы дешифратора прямые.

Два шифратора 4 на 2, с инверсными выходами, выходы подключить к схеме сравнения, выполняющую функцию «равно»

Приоритетный шифратор на 14 входов, предусмотреть сигнал разрешения работы, выходы инверсные.

выбрать самостоятельно

Дешифратор 4 на 10, входы и выходы инверсные, предусмотреть два входа для сигналов условия разрешения работы

Два линейных шифратора 8 на 3 с инверсными входами, выходы которых подключены к элементу сравнения «больше».

самостоятельно

Дешифратор 4 на 12, входы инверсные, выходы прямые

критерию минимального количества корпусов

Два приоритетных шифратора 6 на 3, работающих на три общие линии с логикой подключения выходов к линии.

самостоятельно, обосновать выбор

Дешифратор 3-8 входы и выходы инверсные, выходы дешифраторы должны с помощью схемы разрешения подключаться к одной линии связи.

самостоятельно, обосновать выбор

На базе дешифраторов разработать схему разрешения работы одного элемента логического элемента 3-И-НЕ из матрицы подобных элементов размером 5 на 5

самостоятельно, обосновать выбор

Построить из двух приоритетных шифраторов 8 на 3 приоритетный шифратор 16 на 4. Выходы и входы схемы прямые.

самостоятельно, обосновать выбор

Схема на базе дешифратора 4 на 16

входы инверсные, состояние выходов индицируются светодиодами.

самостоятельно, обосновать выбор

Схема содержит два шифратора 8 на 3 с инверсными входами, выходы шифраторов подключены к логической схеме 8ИЛИ-НЕ

самостоятельно, обосновать выбор

Содержание отчета

Электрическая функциональная схема устройства.

Электрическая принципиальная схема устройства в заданном элементном базисе или выбранном элементном базисе. Если микросхемы выбирались по заданию самостоятельно, обосновать выбор применяемых интегральных схем.

Таблица истинности, справочная информация, временная диаграмма или иная информация необходимая для пояснения работы разработанных функциональной и принципиальной схем.

Для подготовки функциональных и принципиальных схем использовать программу MicroCap8 или Microsoft Visio.

Слева вертикально размещены триггеры двоично – десятичного счетчика. Каждый из триггеров имеет два выхода – прямой и инверсный (

Дешифраторы и индикаторы

Для удобства использования оператором число, записанное в регистре или счетчике в двоичной системе необходимо перевести в удобную форму записи в виде арабских цифр. Данная операция производится с помощью дешифраторов, которые превращают двоичную запись так, чтобы на каком – либо индикаторе отображалась та или другая цифра. Рассмотрим для начала принцип построения индикаторов.

Рассмотрим на примере жидкокристаллического индикатора, который широко применяется в микрокалькуляторах, электронных часах и прочих устройствах. Схема этого индикатора приведена ниже:

Под действием электрического поля сем элементов, которые создают цифру «8», путем изменения своей прозрачности. Если к примеру, подать напряжение между элементом 0 и тремя соединенными вместе элементами 2,3,5, получим цифру 7, при соединении вместе элементов 3 и 5 получим 1. При различных комбинациях будет получать различные цифры на табло.

В цифровых вольтметрах и прочих лабораторных установках широко применяют газоразрядные индикаторы, показанные ниже:

Одна из возможных схем дешифратора приведена ниже:

Слева вертикально размещены триггеры двоично – десятичного счетчика. Каждый из триггеров имеет два выхода – прямой и инверсный (

Приведенная выше схема соединения (с учетом пунктирных связей) обеспечивает данные требования. Так, при записи в триггерах цифры 5 (в двоичном коде 0101), на выходе первого разряда будем иметь

Внимательно присмотревшись к схеме соединения увидим, что у всех логических элементов кроме пятого, хоть на одном из четырех входов будет ноль, а поэтому и на их выходах будут нули, и только у пятого элемента на всех четырех входах будут единицы. Можно убедится, что и при других цифрах в счетчике логическая единица будет только на соответствующем электроде индикатора. Стоит учесть, что дешифратор построен для счетчиков с естественным порядком подсчета.

Источник — http://studme.org/1780030928285/tovarovedenie/deshifratory_shifratory

Источник — http://portal-ed.ru/index.php/osnovy-tsifrovoj-tekhniki/181-shifratory-i-deshifratory

Источник — http://audioakustika.ru/node/1571

Источник — http://tehnar.net.ua/sintez-rabotyi-shifratora/amp/

Источник — http://principraboty.ru/princip-raboty-shifratora/

Источник — http://thelib.info/ekologiya/37129-shifratory-i-deshifratory-naznachenie-ustrojstvo-oblast-primeneniya-tipovye-integralnye-shemy-shifratorov-i-deshifratorov/

Источник — http://studbooks.net/2338471/tehnika/printsip_raboty_deshifratora

Источник — http://studydocs.ru/studfiles/100/916/651529/%D0%BB%D0%B0%D0%B12.doc.html

Источник — http://principraboty.ru/princip-raboty-deshifratora/